Logic-in-Memory Non-Volatile FPGA Design Using Magnetic Tunnel Junctions (Computer Engineering Capstone Project - CE 392)

This project explored the integration of Magnetic Tunnel Junctions (MTJs) into FPGA logic cells to enable non-volatile, in-memory computing: a promising direction for future high-performance, energy-efficient systems. By embedding MTJs directly into configurable logic blocks, we eliminated the need for separate memory and computation modules, resulting in lower latency and improved energy efficiency.

The work was completed using a full-custom digital design flow with the 45nm NCSU FreePDK. Starting from schematic-level simulation, we progressed through layout design, parasitic extraction, and post-layout simulation. Our design featured a 4-input multiplexer integrated with MTJ-based memory latches and optimized clock gating structures. Extensive simulations ensured the circuit maintained correct functionality and acceptable performance even with spintronic components modeled in a primarily CMOS environment.

The final design met our area and power goals while achieving robust performance during write and read cycles. Additionally, we developed custom simulation waveforms, testbenches, and behavioral models to support verification of logic-in-memory concepts. This work provides a scalable foundation for future research on integrating non-traditional memory into reconfigurable architectures, laying the groundwork for a new generation of energy-aware FPGAs.

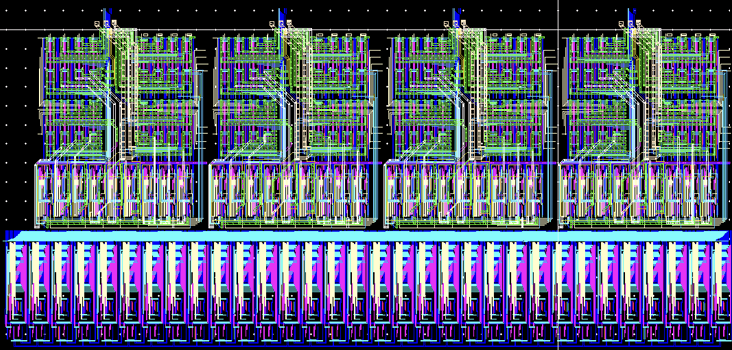

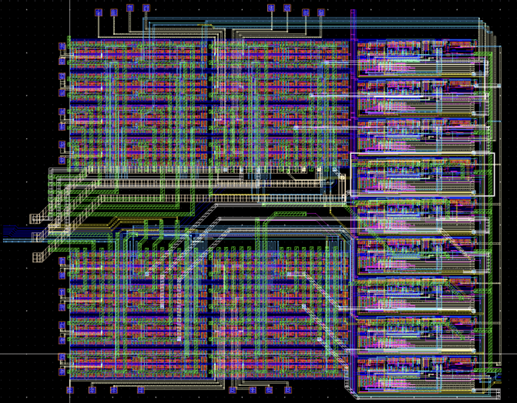

Figure 1: Full Layout

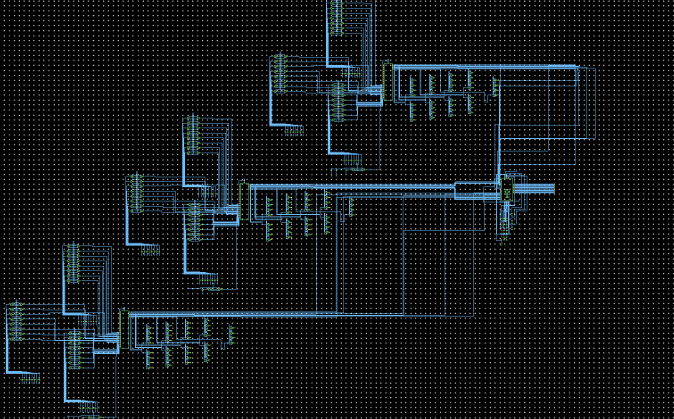

Figure 2: Final Simulation Schematic

Figure 3: 3x3 CLB Layout

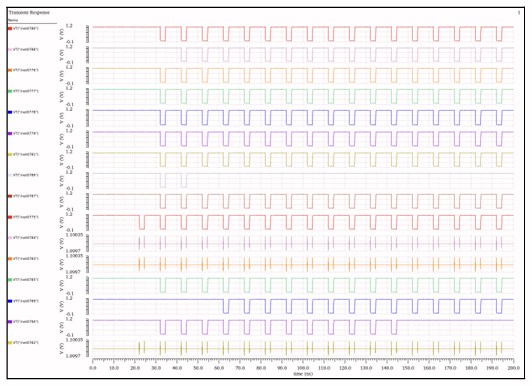

Figure 4: Post-Layout Simulation Results