|

|

|

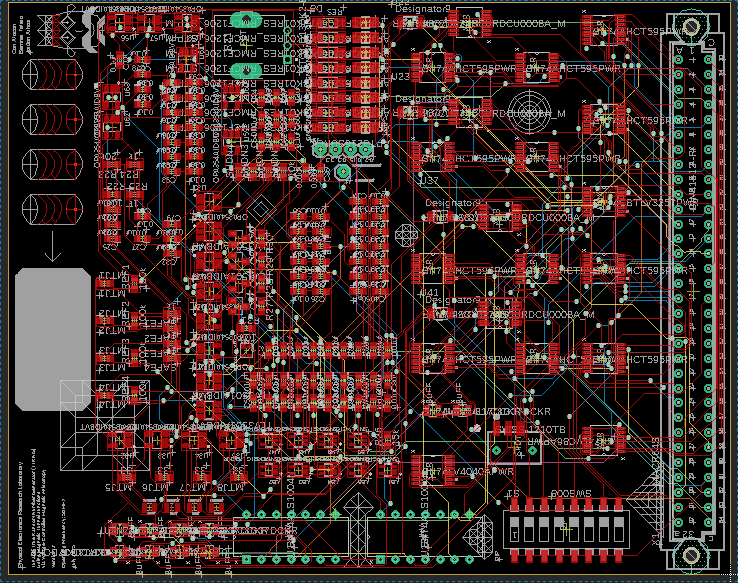

Developed a high-speed true random number generator using MTJs, validated with NIST tests. Designed full-stack PCB hardware, characterized MTJs, and built custom C++ tooling for integration.

View Details

Provided hands-on support to 80+ students in digital logic and LC-3 assembly. Held 150+ hours of office hours and graded lab assignments.

View Details

Managed a $10,000 budget to fund 20+ tech events, workshops, and guest talks. Supported 50+ members and led all finance operations for the chapter.

View Details

Graded weekly assignments for 20 students and held office hours.

View Details

Developing MagSens, a drift- and noise-resilient mixed-signal back-end for Hall-effect magnetic sensing that combines a calibrated analog front-end with digital drift and noise suppression. In progress.

View Project

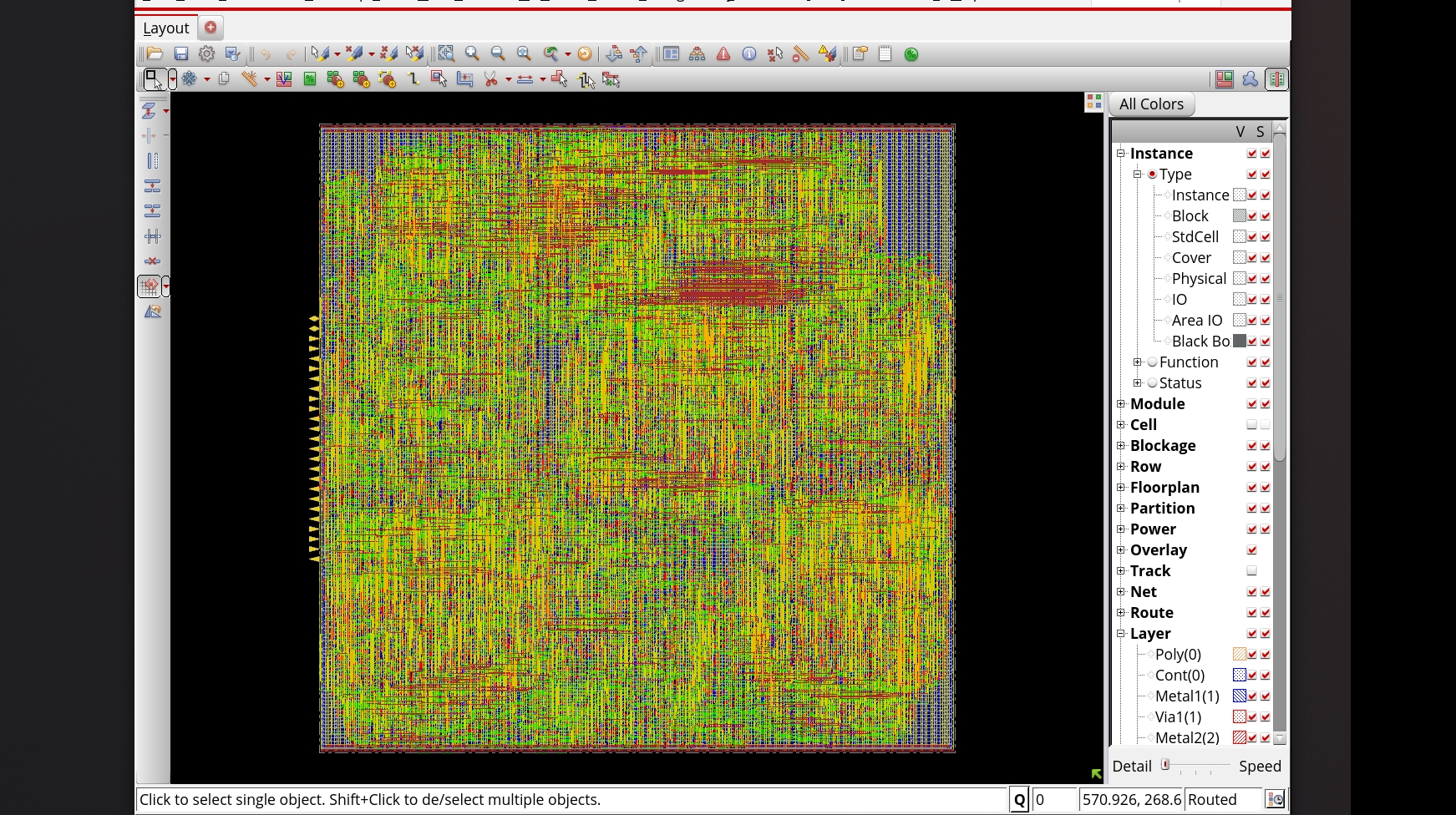

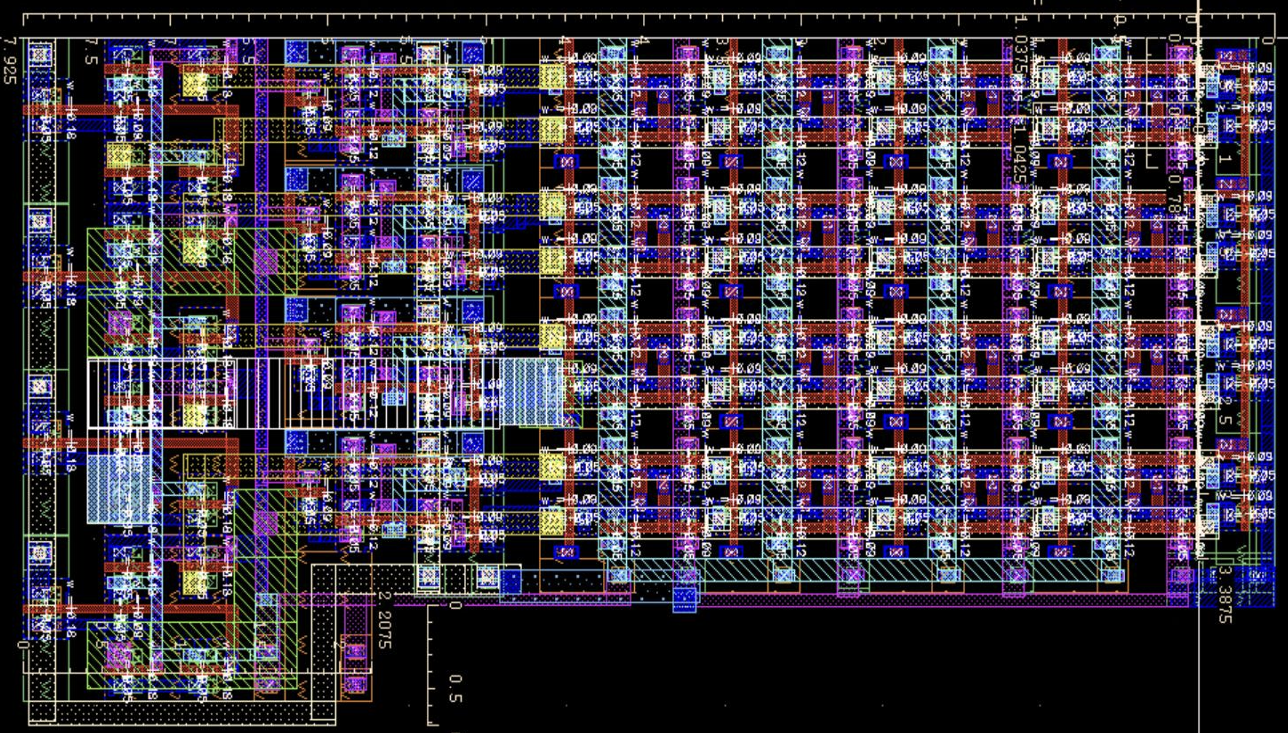

Designed and implemented a digital circuit layout using 45nm technology in a custom CAD flow.

View Project

A 45 nm RV32IM RISC-V with a 5-stage pipeline, synthesized in FreePDK45, integrated with OpenRAM macros.

View Project

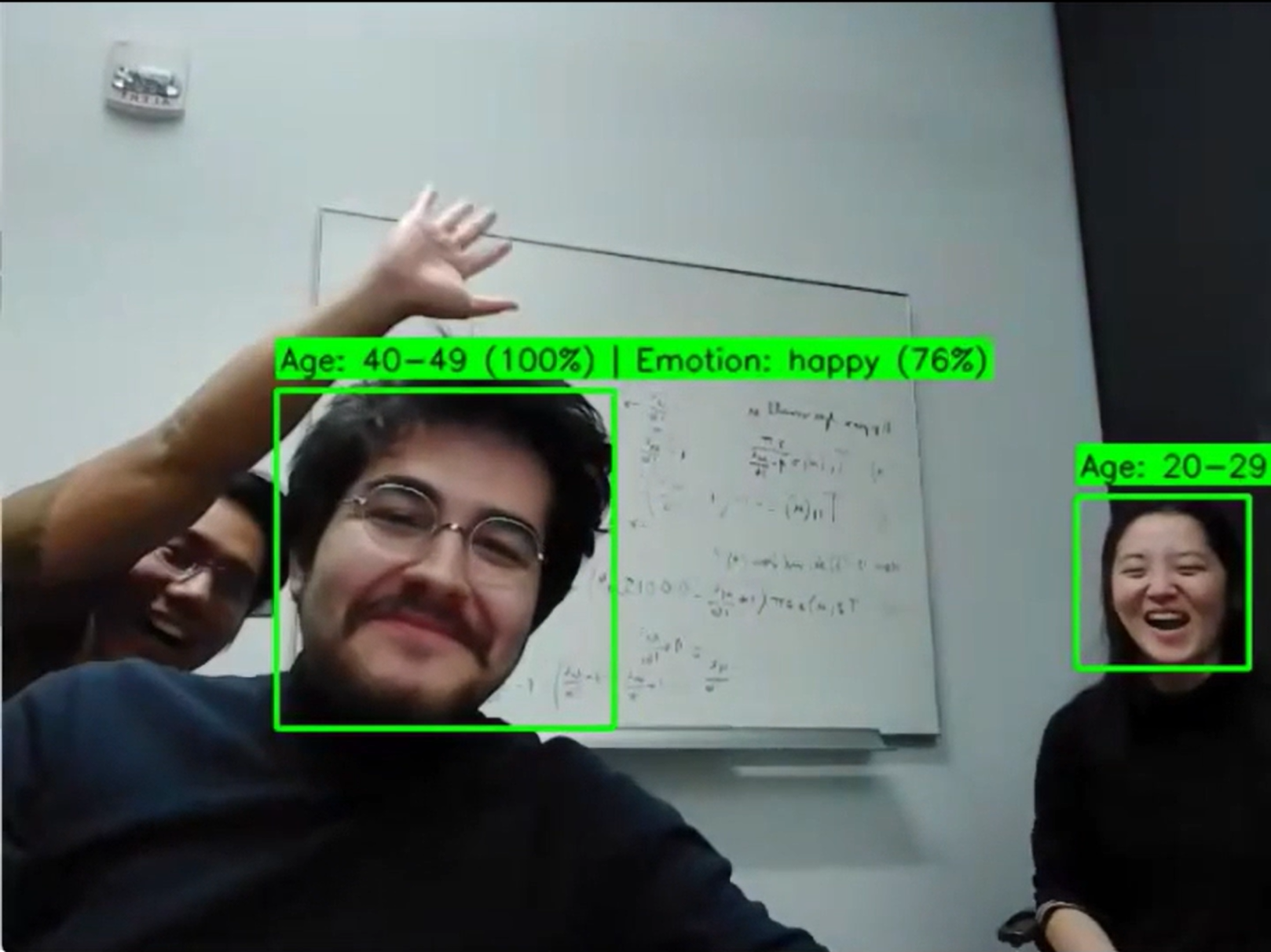

A real-time ML pipeline that detects faces in live video and predicts each face's age group and emotion with confidence-scored overlays.

View Project

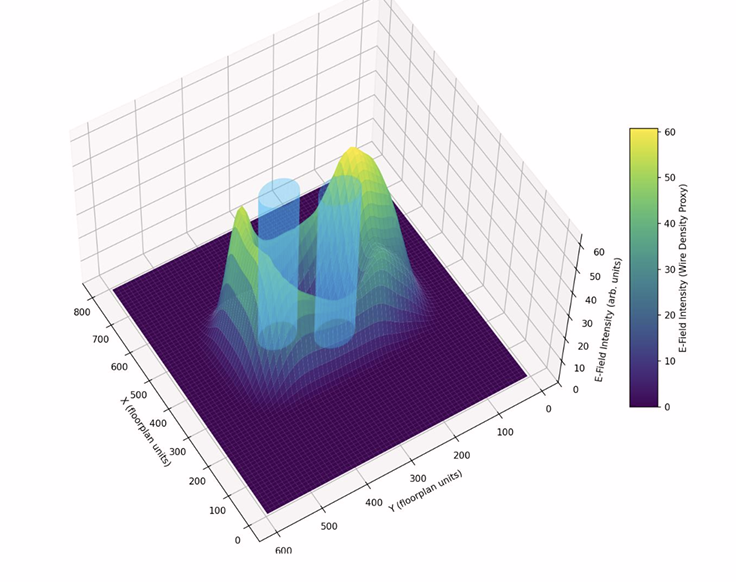

Built a Python tool with GUI and simulated annealing to optimize VLSI floorplans with RF/magnetic constraints.

View Project

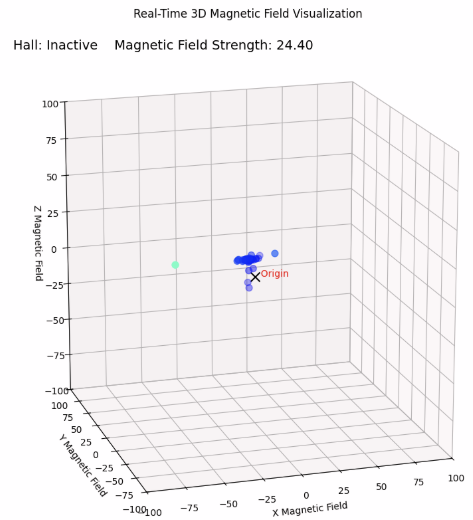

Designed a joystick-controlled AMR scanner with Hall trigger; visualized 3D fields in Python. 3rd place at MMM-Intermag 2025.

View Project

Developed a voice-controlled Flappy Bird game on nRF52833 with RTOS, touchscreen, and MEMS mic integration.

View Project

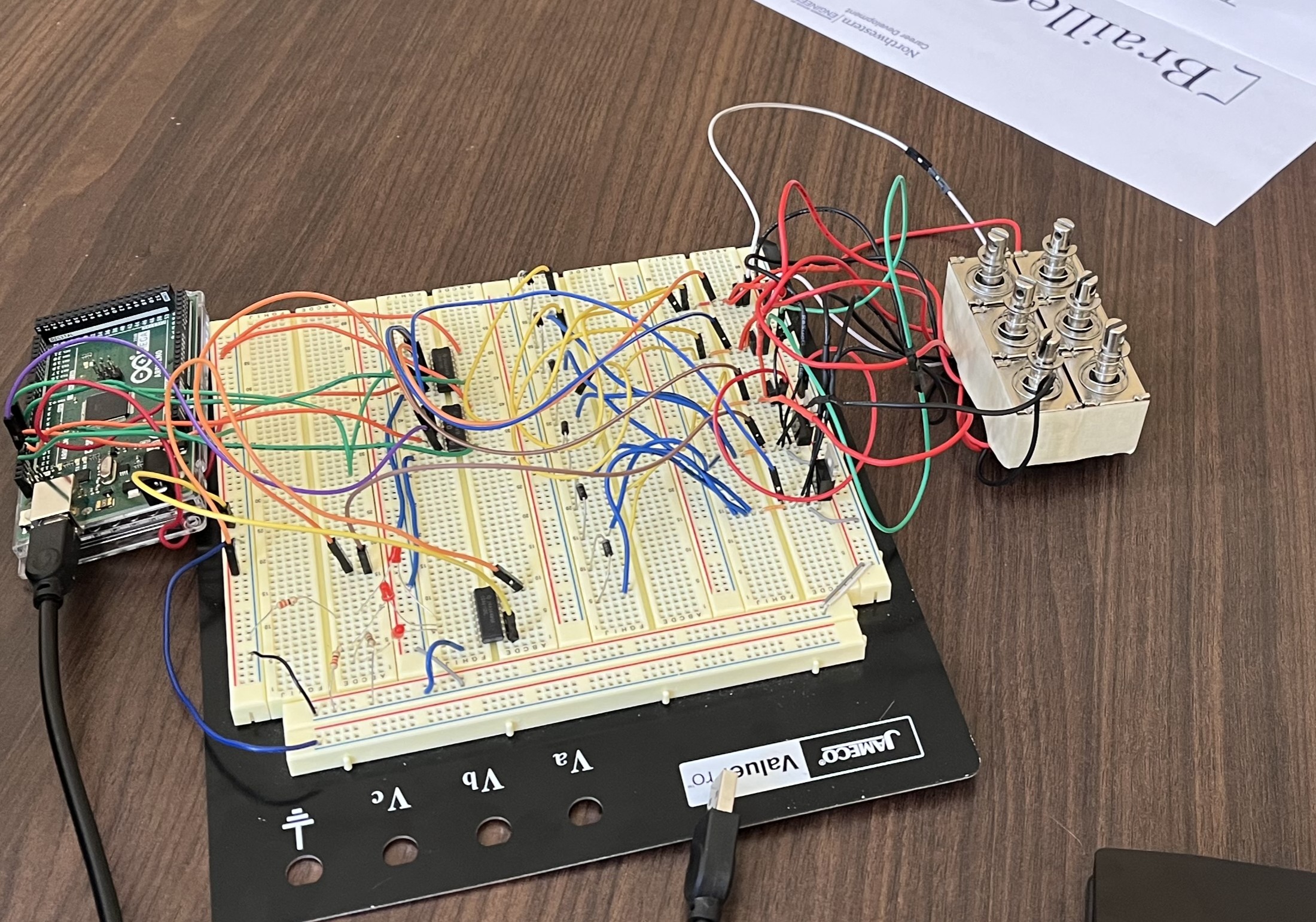

Implemented the Hardware of Grid Actuators for Visually-Impaired Users

View Project

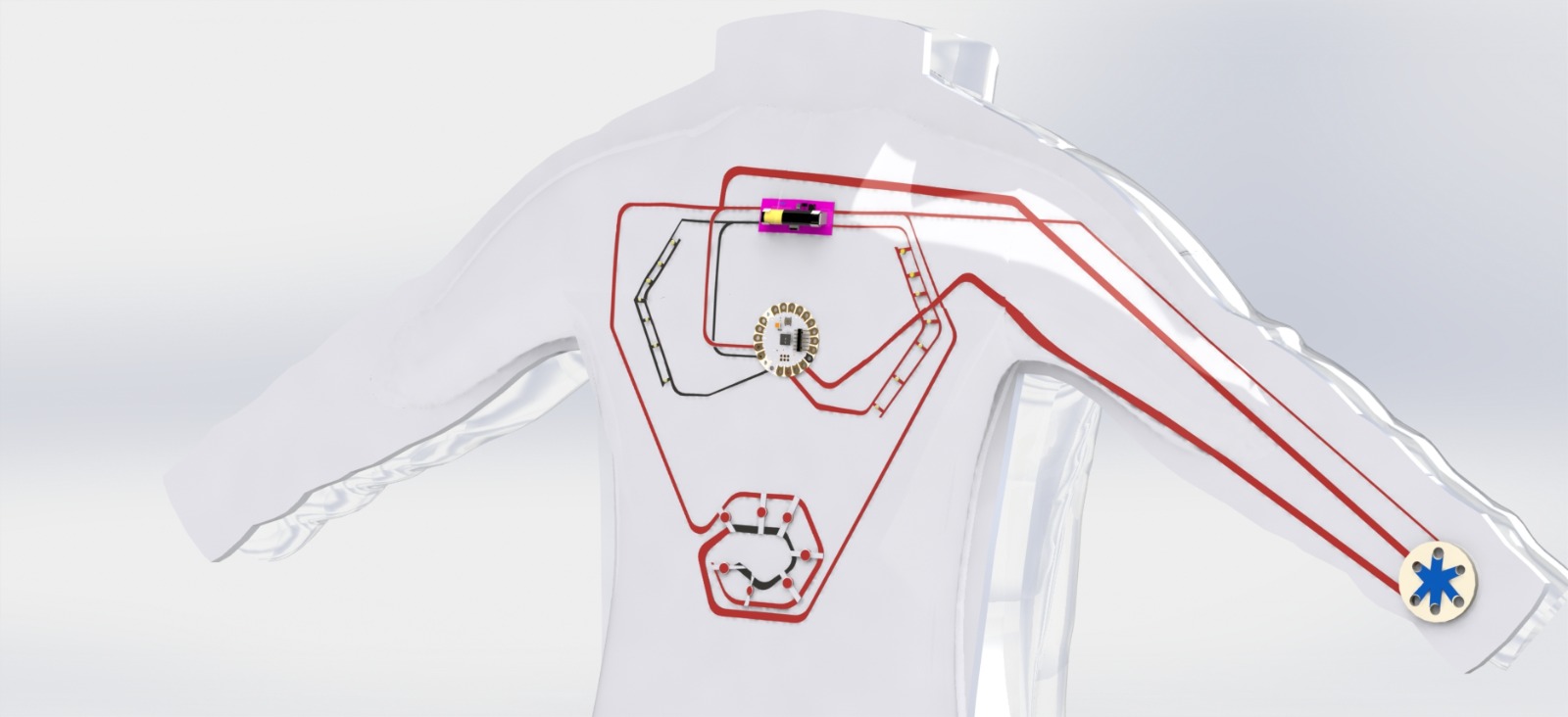

Developed a wearable signaling system using motion sensors for cyclists. Automatically triggers turn signals based on body lean, built in C++ and demonstrated at national competitions.

View Project

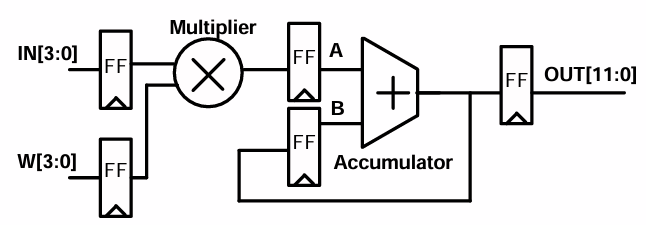

Implemented a pipelined 4-bit signed MAC for ASIC flow; verified with XCelium and synthesized to 28nm.

View Project

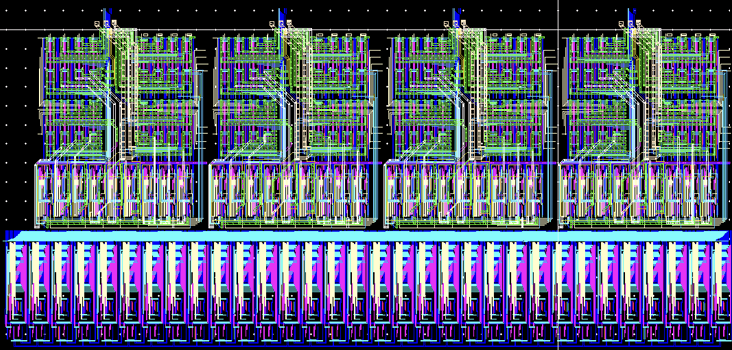

Designed a 4x4-bit SRAM in 45nm CMOS; verified functionality and achieved 500 MHz operation.

View ProjectNorthwestern University • 2026-2027

Northwestern University • 2023-2027

Email: [email protected] Copied!